一、信号完整性分析

(一)DDR 信号仿真(SDRAM ,DDR, , DDR2 ,DDR3,DDR4 …… )

1、DDR 信号完整性及串扰分析

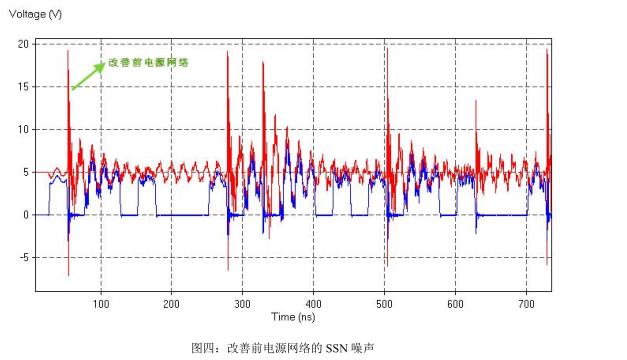

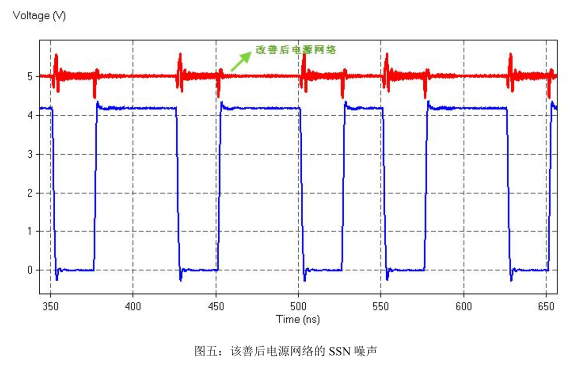

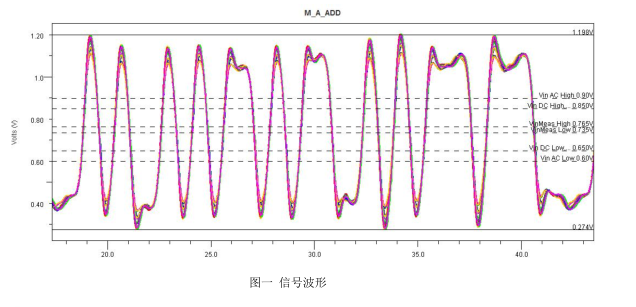

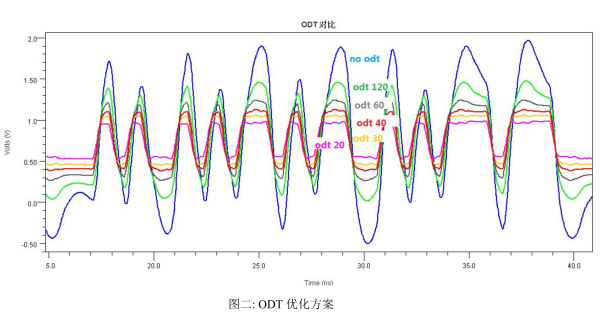

基于仿真模型(IBIS,SPICE 模型等),综合评估 DDR 信号的信号质量,如过冲、振铃、单调性、噪声裕量、ISI(码间干扰)等,合理的优化信号拓扑结构,评估 DDR并行走线的线间串扰情况,并结合仿真结果给出最佳的优化改善方案。

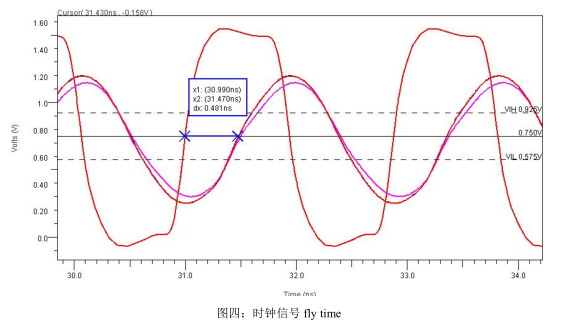

2.、DDR 时序仿真

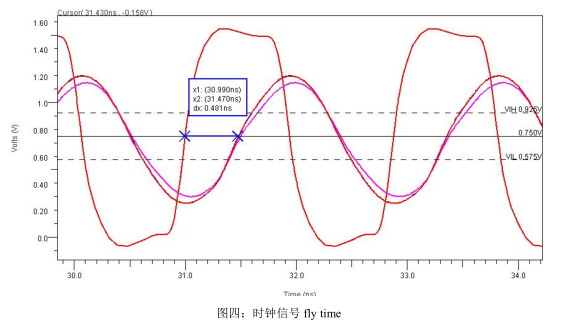

验证 DDR 信号的时序关系(如 DQS&CLK, DQ&DQS, ADD&CLK),制定相关约束条件,给出指导意见,使设计满足系统时序要求。

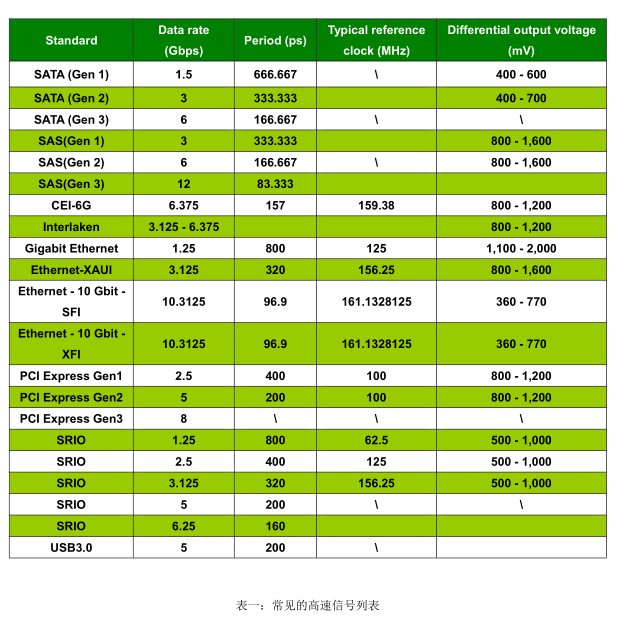

(二)高速串行信号仿真

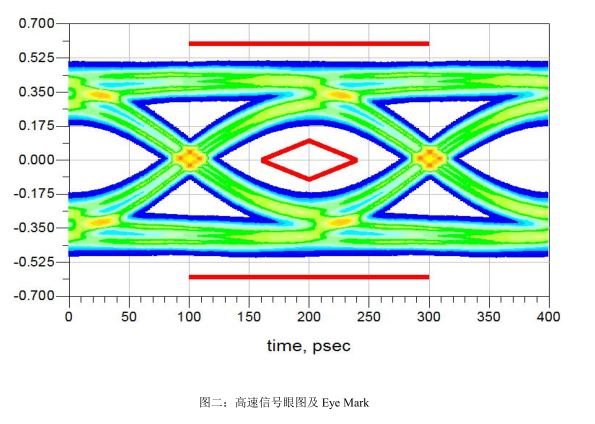

1、高速串行信号完整性分析

常见的高速信号如 PCIE,SATA,GTX,GTP,SRIO,USB3.0,XFP,SFP,XAUI等,评估整条链路上信号从发射端到接收端的表现情况,通过频域上(如 S 参数)和时域上(如信号波形,眼图)的仿真评估,来确保信号的有效传输。

2、高速背板信号完整性分析

通过背板的仿真,可以有效地解决高速信号经过较长背板后由于衰减及反射等信号完整性问题而引起的信号不能有效地进行传输的问题,背板的仿真可以指导客户选择适当的背板材料,并对高速连接器进行优化,有效的降低研发成本,减短设计周期。

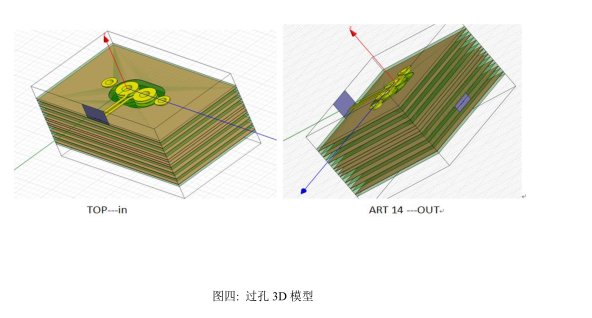

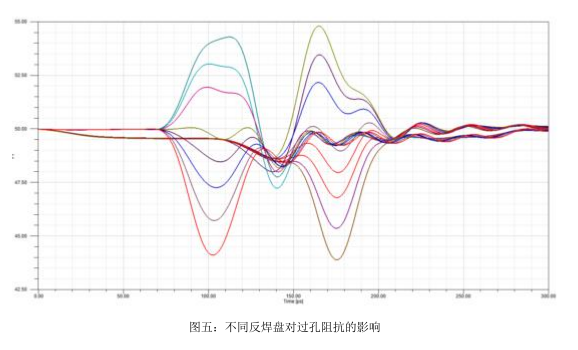

3、过孔优化

对于 PCB 上高速的换层过孔和连接器过孔,通过 3D 软件建模分析,有效地控制过孔阻抗,给出过孔的最优尺寸,从而优化信号质量,提高设计成功率。

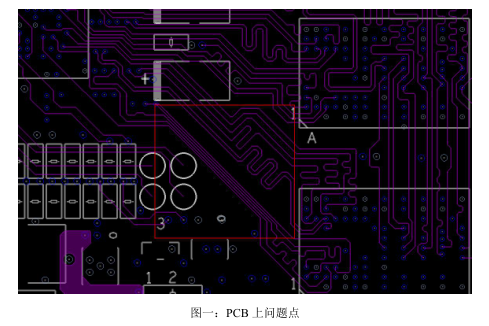

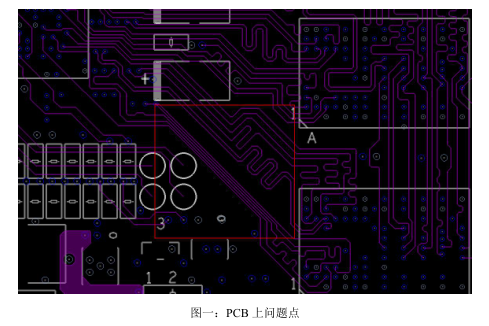

(三)整板串扰分析:

PCB 完成布线后,扫描整个 PCB 的串扰情况,指出串扰较大网络以及干扰源网络,可使设计师有针对性的对 PCB 进行优化,提高设计性能。

(四)拓扑结构优化:

针对复杂的拓扑结构,如 DSP 与 FPGA,FLASH,SDRAM 等相互通信的复杂拓扑,在布局前给出最优的建议,避免信号在通信过程中因为拓扑结构不合理而造成较大发射,串扰等,从而避免因拓扑结构带来的信号完整性问题而引起系统错误。

二、电源完整性分析

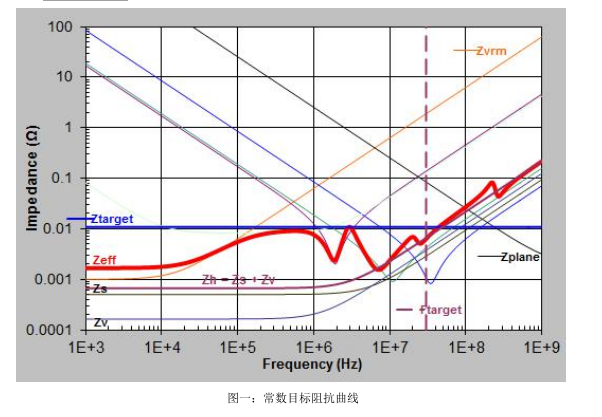

(一)频域阻抗分析

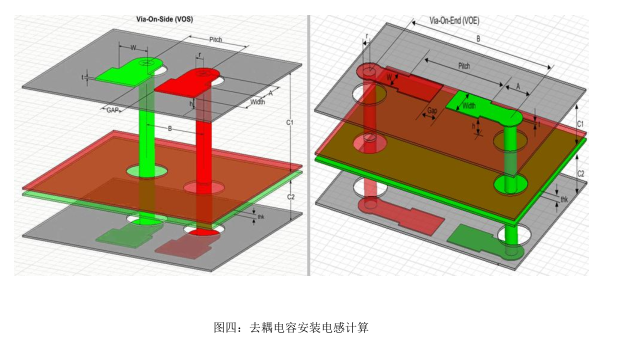

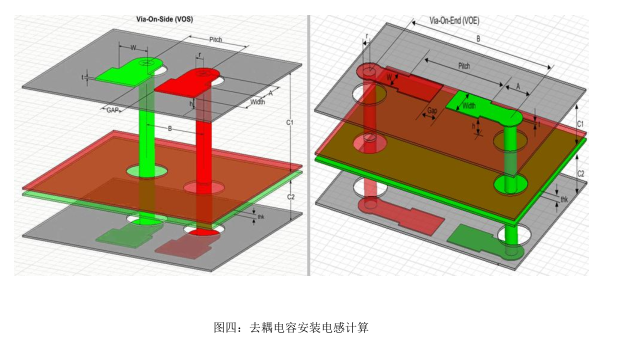

电源阻抗分析是经典的 PI 分析方法,通过分析电源网络的阻抗,来指导优化去耦电容器的大小、数量和位置,从而使芯片管脚处的电源波动稳定在噪声容限之内。

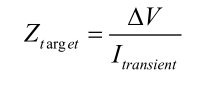

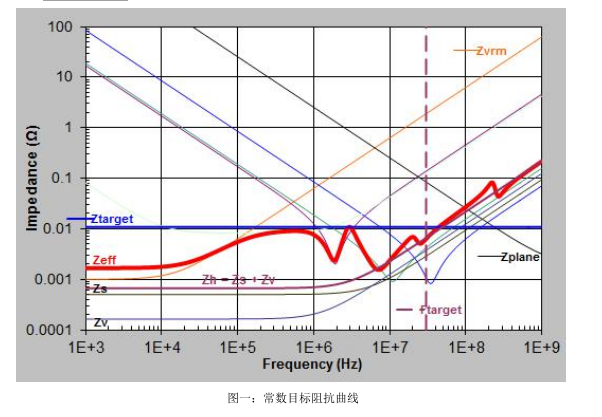

1、常数目标阻抗

估计最坏情况下的最大瞬时电流,从而得到最悲观的目标阻抗,并将其应用在整个板级频带范围内。

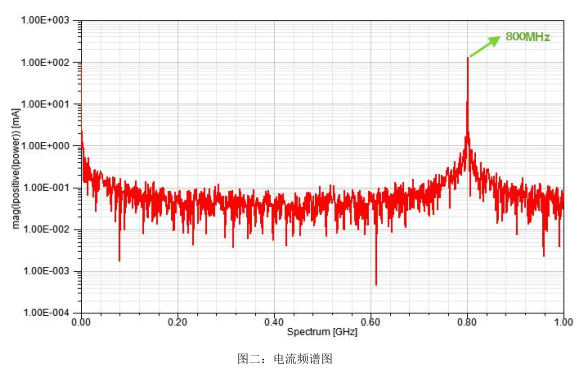

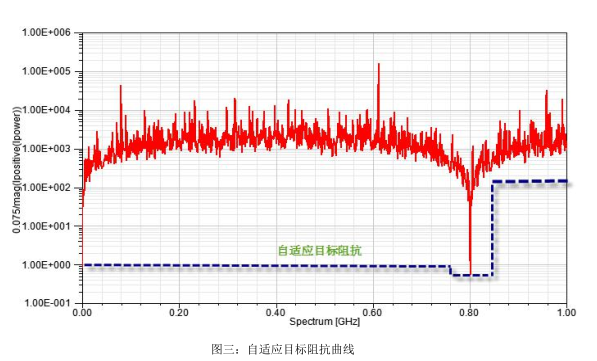

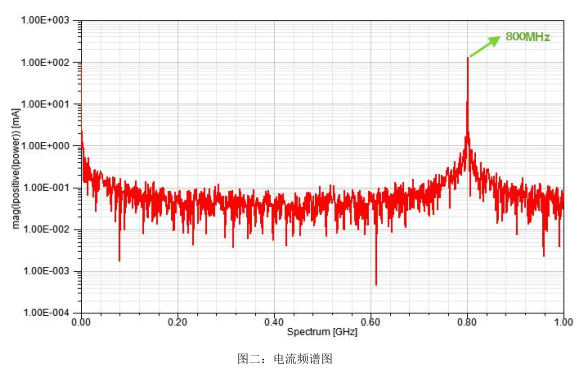

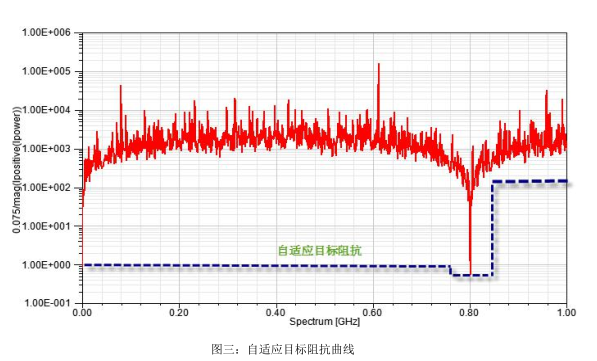

2、自适应目标阻抗

应用 IBIS、SPICE 等模型估计实际情况下的瞬时电流频谱,从而得到自适应目标阻抗,这种估计更接近芯片的实际工作情况,有利于降低成本,减少去耦电容的使用数量。

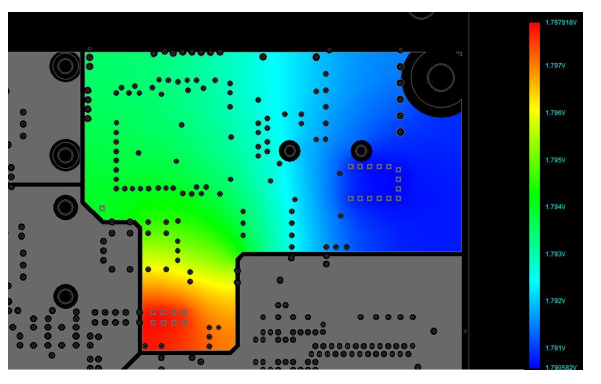

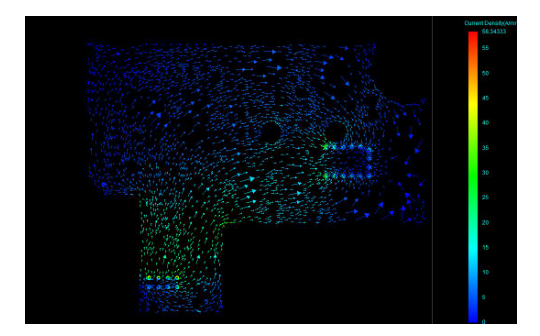

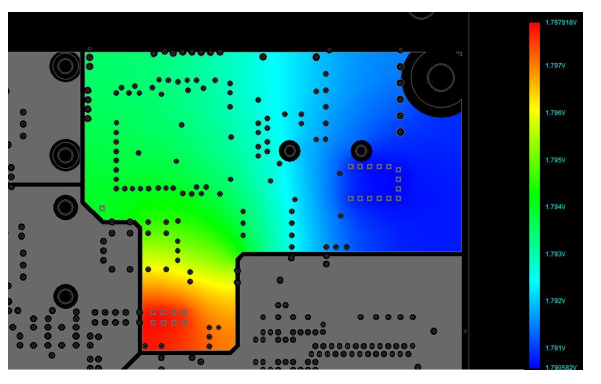

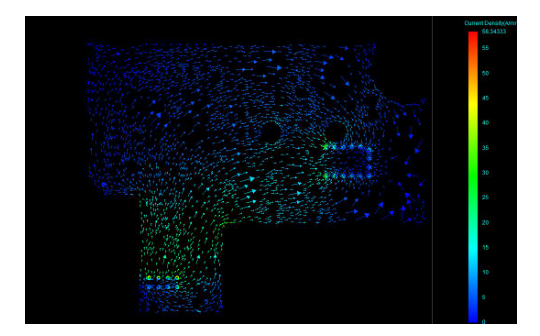

(二)直流电压降分析

(二)直流电压降分析

仿真电源平面层的直流电压降(包括平面电压分布,电流分布),以及过孔、铜皮的电流密度与电流方向,考察平面层的载流能力。

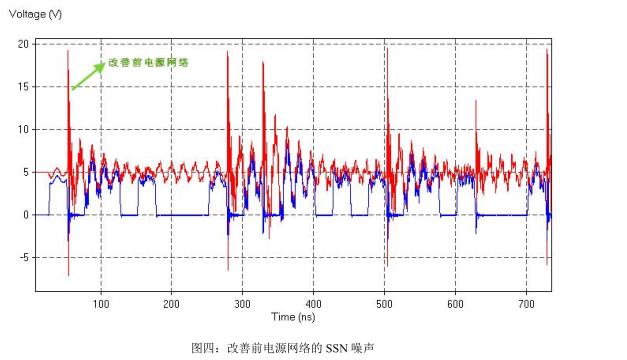

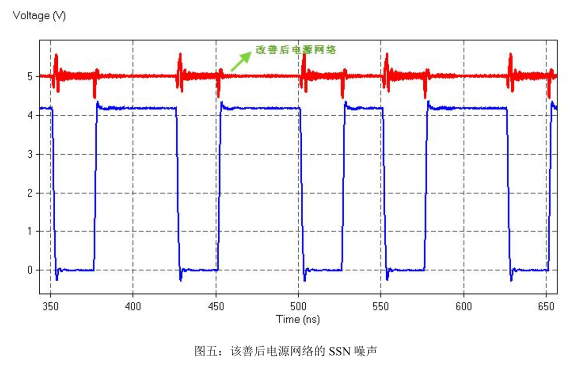

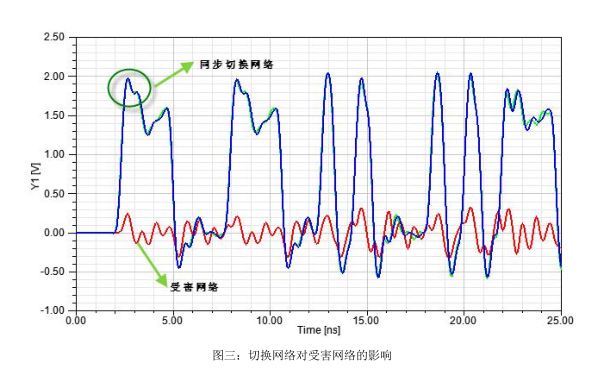

(三)同时开关噪声(SSN

(三)同时开关噪声(SSN

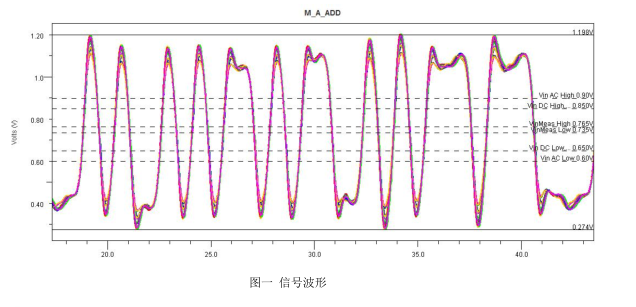

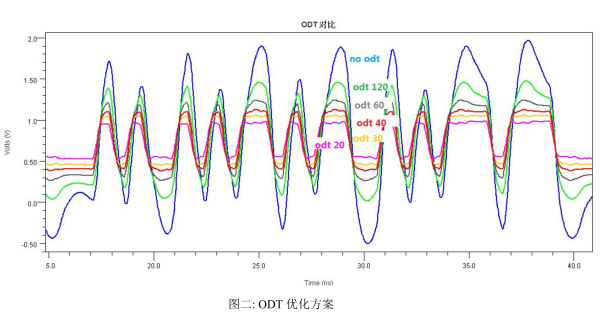

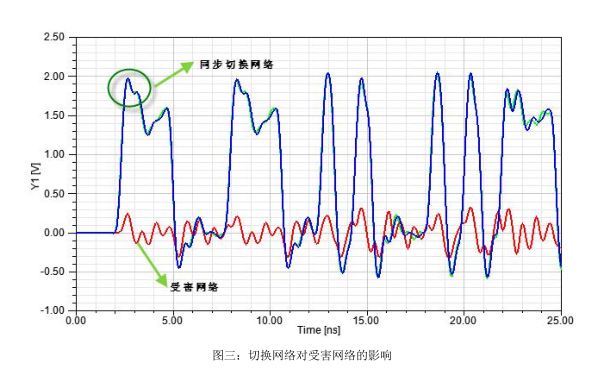

SSN 主要是伴随着器件的同步开关输出(SSO)而产生,开关速度越快,瞬时电流变化越显著。SSN 噪声过大可能会对邻近的信号线造成很大的串扰,使得受害线信号质量下降和时序裕量的减小;SSN 噪声还会通过芯片的电源地管脚耦合到电源地平面,带来电源完整性的问题。

1、SSN-SI 分析

问题定位:

2、SSN-PI 分析